# Sequential Logic Design Principles (2)

### 1. Clocked Synchronous State-Machine Design

- The steps for designing a clocked synchronous state machine, starting from a word description or specification, are just about the reverse of the analysis steps that we used in the previous lecture:

- Construct a state/output table corresponding to the word description or specification, using mnemonic names for the states. (It's also possible to start wit a state diagram)

- 2. (Optional) Minimize the number of states in the state/output table.

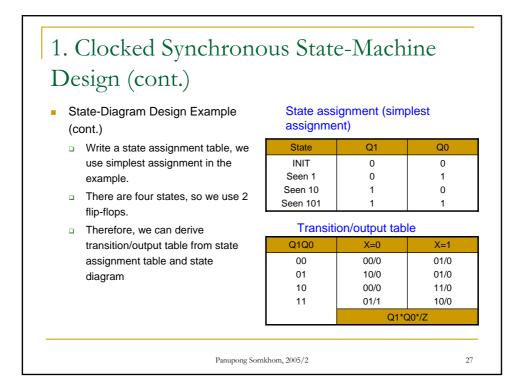

- 3. Choose a set of state variables and assign state-variable communications to the named states.

Panupong Sornkhom, 2005/2

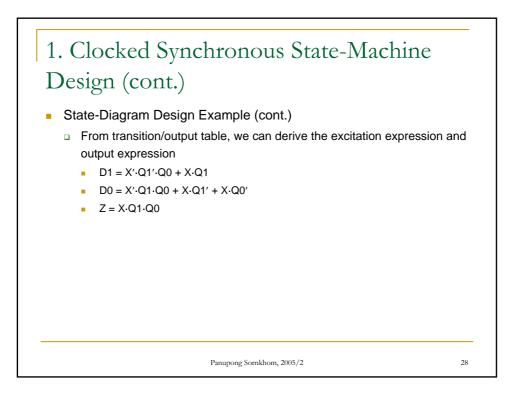

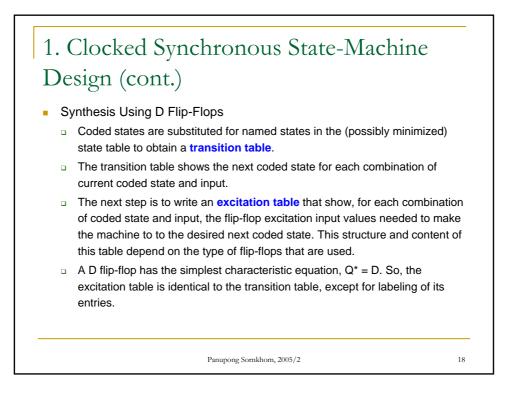

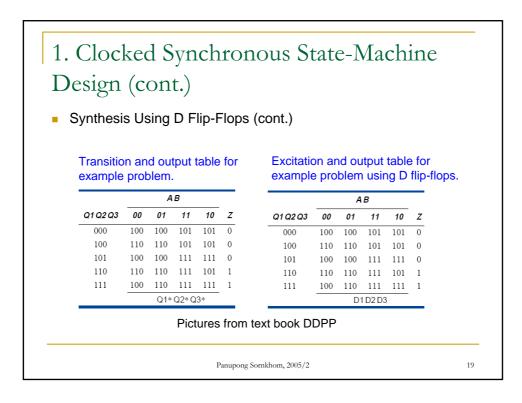

- 4. Substitute the state-variable combinations into the state/output table to create a transition/output table that shows the desired next statevariable combination and output for each state/input combination.

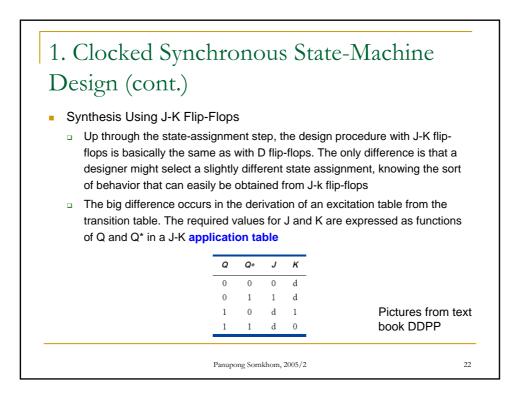

- 5. Choose a flip-flop type (e.g., D or J-K) for the state memory.

- 6. Construct an excitation table that shows the excitation values required to obtain the desired next state for each state/input combination.

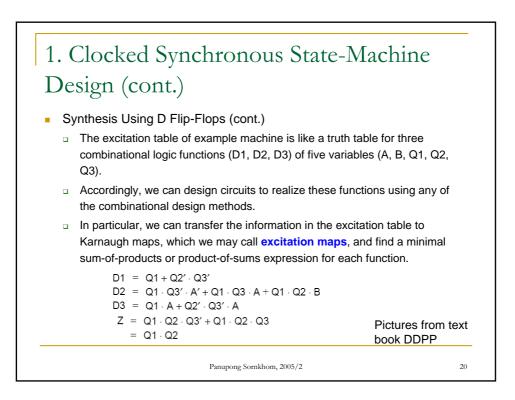

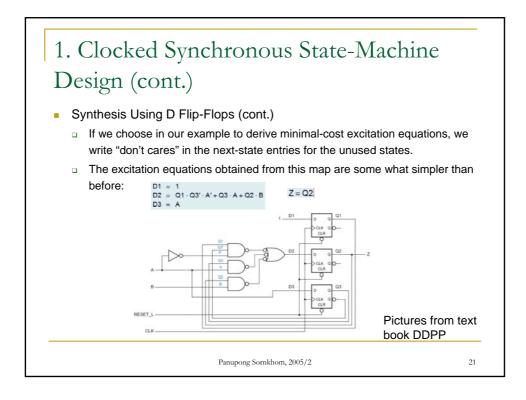

- 7. Derive excitation equations from the excitation table.

- 8. Derive output equations from the transition/output table.

- 9. Draw a logic diagram that shows the state-variable storage elements and realizes the excitation and output equations.

Panupong Sornkhom, 2005/2

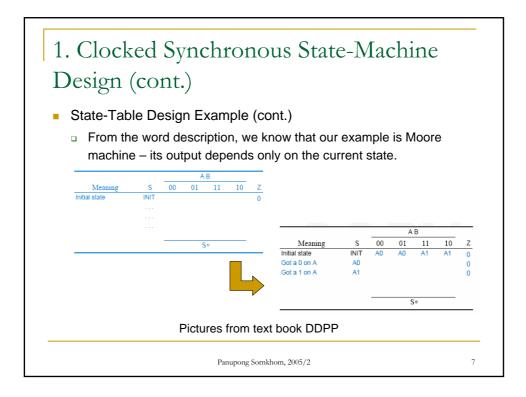

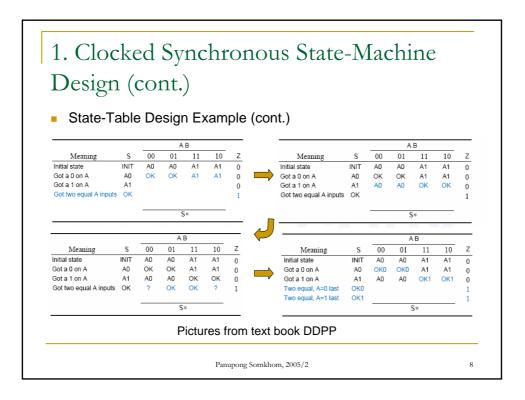

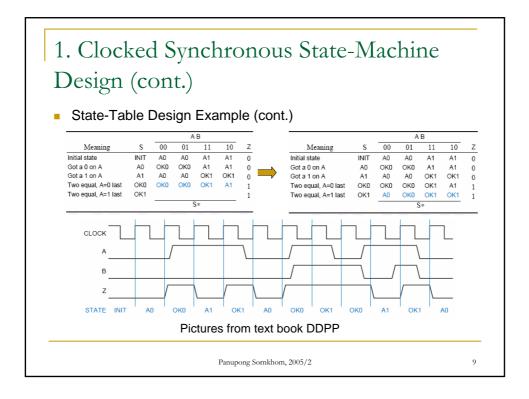

5

1. Clocked Synchronous State-Machine Design (cont.) State-Table Design Example Design a clocked synchronous state machine with two inputs, A and B, and a single output Z that is 1 if: A had the same value at each of the two previous clock ticks, or . B has been 1 since the last time that the first condition was true. . Otherwise, the output should be 0. CLOCK Pictures from text book DDPP Panupong Sornkhom, 2005/2 6

- State Assignment (cont.)

- The simplest assignment of s coded states to 2<sup>n</sup> possible states is to use the first s binary integers in binary counting order

- However, the simplest state assignment does not always lead to the simplest excitation equations, output equations, and resulting logic circuit.

- In fact, the state assignment often has a major effect on circuit cost, and it may interact with other factors.

- So, how do we choose the best assignment for a given problem?

- The only formal way to find the best assignment is to try all the assignments. That's too much work.

Panupong Sornkhom, 2005/2

13

#### 1. Clocked Synchronous State-Machine Design (cont.) Possible state assignments for the example machine Assignment State name Simplest Q1–Q3 Decomposed Q1–Q3 Almost one-hot Q1–Q4 One-hot Q1–Q5 INIT 00001 000 0000 000 A0 001 100 00010 0001 A1 0010 010 101 00100 OK0 01000 011 110 0100 OK1 100 111 10000 1000 Pictures from text book DDPP 14 Panupong Sornkhom, 2005/2

### State Assignment (cont.)

Guidelines for making reasonable state assignments:

- Choose an initial coded state into which the machine can easily be forced at reset (00...00 or 11...11 in typical circuits).

- Minimize the number of state variables that change on each transition

- Maximize the number of state variables that don't change in a group of related states (i.e., a group of states in which most of transitions stay in the group).

- Exploit symmetries in the problem specification and the corresponding symmetries in the state table. That is, suppose that one state or group of states means almost the same thing as another. Once an assignment has been established for the first, a similar assignment, differing only in one bit, should be used for the second.

Panupong Sornkhom, 2005/2

15

State Assignment (cont.)

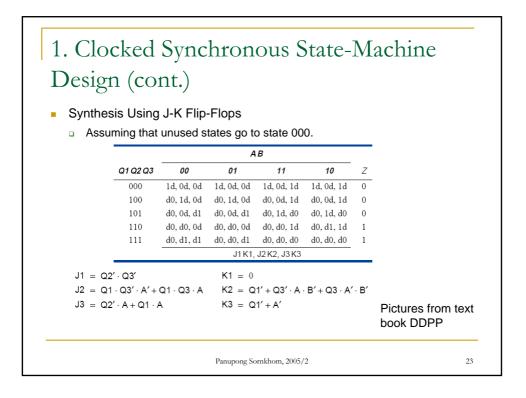

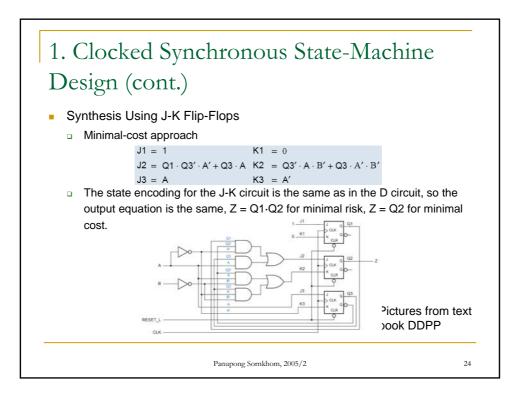

• There are two approaches to handle with **unused states**:

- Minimal risk. This approach assumes that it is possible for the state machine somehow to get into one of the unused (or "illegal") states. Therefore, all of the unused state-variable combinations are identified and explicit next-state entries are made so that, for any input combination, the unused states go to the "initial" state, the "idle" state, or other "safe" state.

- Minimal cost. This approach assumes that the machine will never enter an unused state. Therefore, in the transition and excitation tables, the next-state entries of the unused states can be marked as "don't-cares."

Panupong Sornkhom, 2005/2

17

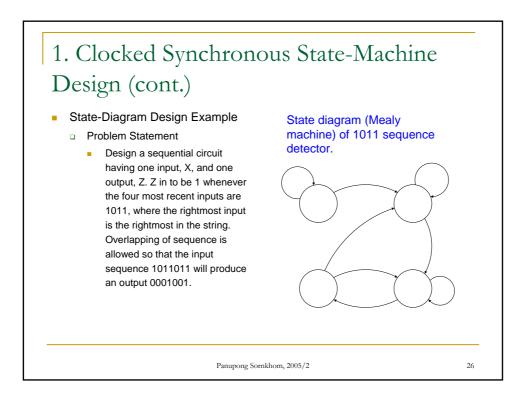

### Designing State Machines Using State Diagram

- State diagrams are often used to design small- to medium-sized state machines

- Designing a state diagram is much like designing a state table which is much like writing a program.

- However, there is one fundamental difference between a state diagram and a state table, a difference that makes state-diagram design simpler but also more error prone:

- A state table is an exhaustive listing of the next states for each state/input combination.

No ambiguity is possible.

- A state diagram contains a set of arcs labeled with transition expressions. Even when there are many inputs, only one transition expression is required per arc. However, when a state diagram is constructed, there is no guarantee that the transition expressions written on the arcs leaving a particular state cover all input combinations exactly once.

Panupong Sornkhom, 2005/2

25